# PIC Peripherals

Dr. Altaf Osman Mulani E&TC Department SKN SINHGAD COLLEGE OF ENGG., KORTI, PANDHARPUR

## **Course Outcomes**

| Course Name   | :Microcontrollers & Applications              | <b>Course Code:</b>                                                       | : ET312          |                              |  |  |  |

|---------------|-----------------------------------------------|---------------------------------------------------------------------------|------------------|------------------------------|--|--|--|

| Class         | :Third Year B.Tech.                           | Semester                                                                  | : I              |                              |  |  |  |

| Academic Year | :202223                                       | Subject<br>Teacher                                                        | : Dr. A. O. Mula | ni                           |  |  |  |

| CO No.        | Course Ou                                     | tcome Statements                                                          |                  | Cognitive<br>Level           |  |  |  |

| ET312.1       | To recognize the fundamental features and ope | eration of contemporary m                                                 | icrocontroller   | Remember,<br>Understand      |  |  |  |

| ET312.2       | To illustrate the hardware interfacing.       | Understar Apply, Analyze, Create                                          |                  |                              |  |  |  |

| ET312.3       | To discuss the fundamentals of CISC and RIS   | C Microcontroller architec                                                | etures           | Remember,<br>Understand      |  |  |  |

| ET312.4       | To discuss various core and peripheral feat   | To discuss various core and peripheral features in microcontroller family |                  |                              |  |  |  |

| ET312.5       | To demonstrate the programs in assembly lang  | guage and C language for 1                                                | microcontrollers | Understand,<br>Apply, Create |  |  |  |

### ADCONO register (address 1FH)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0         | R/W-0 |

|-------|-------|-------|-------|-------|---------|-------------|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | <del></del> | ADON  |

| bit 7 | 1     | 1     |       |       | •       |             | bit 0 |

ADC\$1:ADC\$0: A/D Conversion Clock Select bits (ADCON0 bits in bold)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adc\$1:adc\$0></adc\$1:adc\$0> | Clock Conversion                                        |

|---------------------------|-------------------------------------------|---------------------------------------------------------|

| 0                         | 00                                        | Fosc/2                                                  |

| 0                         | 01                                        | Fosc/8                                                  |

| 0                         | 10                                        | Fosc/32                                                 |

| 0                         | 11                                        | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                        | Fosc/4                                                  |

| 1                         | 01                                        | Fosc/16                                                 |

| 1                         | 10                                        | Fosc/64                                                 |

| 1                         | 11                                        | FRC (clock derived from the internal A/D RC oscillator) |

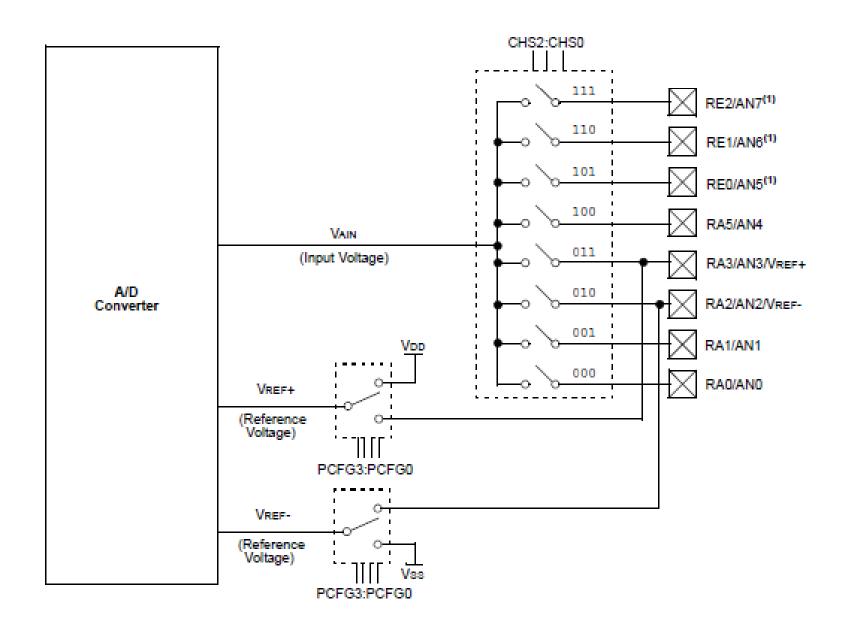

#### bit 5-3 CHS2:CHS0: Analog Channel Select bits

- 000 = Channel 0 (AN0)

- 001 = Channel 1 (AN1)

- 010 = Channel 2 (AN2)

- 011 = Channel 3 (AN3)

- 100 = Channel 4 (AN4)

- 101 = Channel 5 (AN5)

- 110 = Channel 6 (AN6)

- 111 = Channel 7 (AN7)

- bit 2 GO/DONE: A/D Conversion Status bit

#### When ADON = 1:

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion which is automatically cleared by hardware when the A/D conversion is complete)

- 0 = A/D conversion not in progress

- bit 1 Unimplemented: Read as '0'

- bit 0 ADON: A/D On bit

bit 7-6

- 1 = A/D converter module is powered up

- 0 = A/D converter module is shut-off and consumes no operating current

### ADCON1 register (address 9FH):

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-----|-----|-------|-------|-------|-------|

| ADFM  | ADCS2 | _   | _   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 | -     | -   |     |       |       |       | bit 0 |

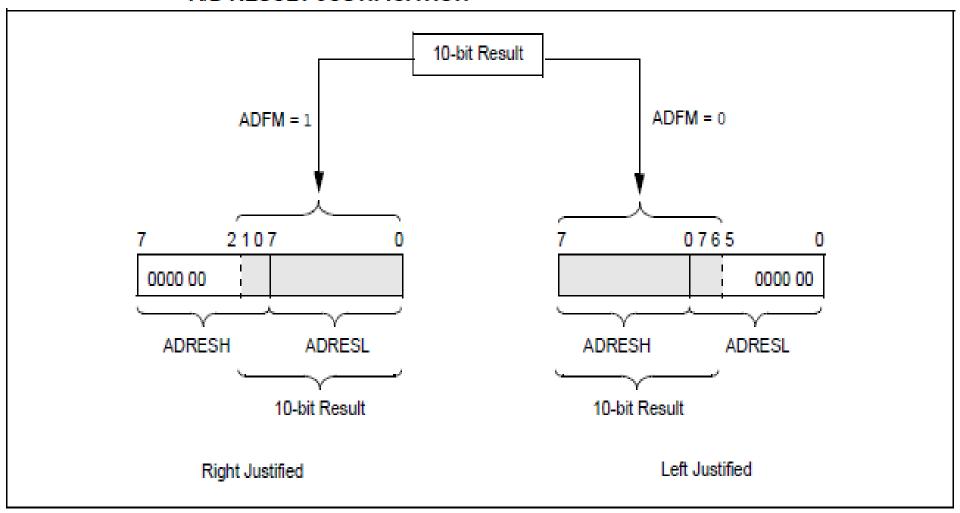

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. Six (6) Most Significant bits of ADRESH are read as '0'.

0 = Left justified. Six (6) Least Significant bits of ADRESL are read as '0'.

bit 5-4 Unimplemented: Read as '0'

bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits

| PCFG<br><3:0> | AN7 | AN6 | AN5 | AN4 | AN3   | AN2   | AN1 | AN0 | VREF+ | VREF- | C/R |

|---------------|-----|-----|-----|-----|-------|-------|-----|-----|-------|-------|-----|

| 0000          | Α   | Α   | Α   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 8/0 |

| 0001          | Α   | Α   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 7/1 |

| 0010          | D   | D   | D   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 5/0 |

| 0011          | D   | D   | D   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 4/1 |

| 0100          | D   | D   | D   | D   | Α     | D     | Α   | Α   | VDD   | Vss   | 3/0 |

| 0101          | D   | D   | D   | D   | VREF+ | D     | Α   | Α   | AN3   | Vss   | 2/1 |

| 011x          | D   | D   | D   | D   | D     | D     | D   | D   | _     | _     | 0/0 |

| 1000          | Α   | Α   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 6/2 |

| 1001          | D   | D   | Α   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 6/0 |

| 1010          | D   | D   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 5/1 |

| 1011          | D   | D   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 4/2 |

| 1100          | D   | D   | D   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 3/2 |

| 1101          | D   | D   | D   | D   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 2/2 |

| 1110          | D   | D   | D   | D   | D     | D     | D   | Α   | VDD   | Vss   | 1/0 |

| 1111          | D   | D   | D   | D   | VREF+ | VREF- | D   | Α   | AN3   | AN2   | 1/2 |

A = Analog input D = Digital I/O

C/R = # of analog input channels/# of A/D voltage references

#### A/D RESULT JUSTIFICATION

### **ADC Conversion:**

### Follow these steps A/D Conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCONO)

- Select A/D conversion clock (ADCONO)

- Turn on A/D module (ADCONO)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIF bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCONO)

- 5. Wait for A/D conversion to complete.

- 6. Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

| #INCLUDE <p16f877a.inc></p16f877a.inc> | BSF INTCON,GIE     |

|----------------------------------------|--------------------|

| RO EQU 20H                             | BSF INTCON, PEIE   |

| BSF STATUS,RPO                         | BSF PIE1,ADIE      |

| MOVLW 80H                              | BSF ADCONO,GO      |

| MOVWF ADCON1                           |                    |

| MOVLW 3FH                              | A2:DECFSZ R0       |

| MOVWF TRISA                            | GOTO A2            |

| MOVLW 07H                              |                    |

| MOVWF TRISE                            | A3:BTFSC ADCON0,GO |

| CLRF TRISB                             | GOTO A3            |

| CLRF TRISD                             | F0:MOVF ADRESH,W   |

| BCF STATUS, RPO                        | MOVWF PORTB        |

|                                        | MOVF ADRESL,W      |

| MOVLW 81H                              | MOVWF PORTD        |

| MOVWF ADCONO                           | RETURN             |

| A1:BCF PIR1,ADIF                       | END                |

| BSF STATUS,RPO                         |                    |

## **ADC**

# Types of Oscillator

- PIC16F877A can be operated in four different oscillator modes.

- The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- ▶ LP Low-Power Crystal (5 200 KHz)

- XT Crystal/Resonator (100 KHz 4 MHz)

- HS High-Speed Crystal/Resonator (4 20 MHz)

- RC Resistor/Capacitor (0 − 4 MHz)

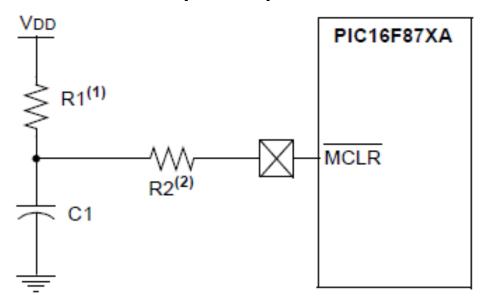

## Types of reset

Power On Reset (POR)

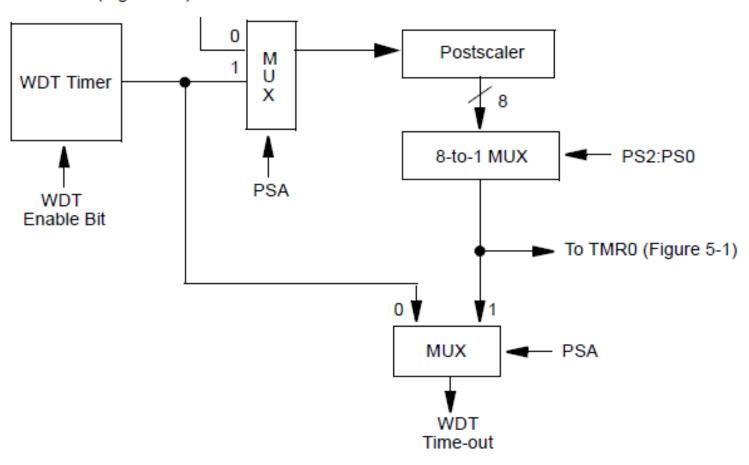

## Watchdog Timer

From TMR0 Clock Source (Figure 5-1)

Note: PSA and PS2:PS0 are bits in the OPTION\_REG register.

# Watchdog Timer

| Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | Fosc1 | Fosc0 |

| OPTION_REG   | RBPU  | INTEDG               | T0CS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

# PIE1 Register

| PSPIE <sup>(1)</sup> | ADIE | RCIE | TXIE | SSPIE | CCP1IE | TMR2IE | TMR1IE |

|----------------------|------|------|------|-------|--------|--------|--------|

| hit 7                |      |      |      |       |        |        | hit ∩  |

| PSPIE: Parallel Slave Port Read/Write Interrupt Enable bit |

|------------------------------------------------------------|

| 1 = Enables the PSP read/write interrupt                   |

| 0 = Disables the PSP read/write interrupt                  |

| ADIE: A/D Converter Interrupt Enable bit                   |

| 1 = Enables the A/D converter interrupt                    |

| 0 = Disables the A/D converter interrupt                   |

| RCIE: USART Receive Interrupt Enable bit                   |

| 1 = Enables the USART receive interrupt                    |

| 0 = Disables the USART receive interrupt                   |

| TXIE: USART Transmit Interrupt Enable bit                  |

| 1 = Enables the USART transmit interrupt                   |

| 0 = Disables the USART transmit interrupt                  |

| SSPIE: Synchronous Serial Port Interrupt Enable bit        |

| 1 = Enables the SSP interrupt                              |

| 0 = Disables the SSP interrupt                             |

| CCP1IE: CCP1 Interrupt Enable bit                          |

| 1 = Enables the CCP1 interrupt                             |

| 0 = Disables the CCP1 interrupt                            |

| TMR2IE: TMR2 to PR2 Match Interrupt Enable bit             |

| 1 = Enables the TMR2 to PR2 match interrupt                |

| 0 = Disables the TMR2 to PR2 match interrupt               |

| TMR1IE: TMR1 Overflow Interrupt Enable bit                 |

| 1 = Enables the TMR1 overflow interrupt                    |

| 0 = Disables the TMR1 overflow interrupt                   |

## PIR1 Register

| PSPIF(1) | ADIF | RCIF  | TXIF  | SSPIF | CCP1IF  | TMR2IF        | TMR1IF     |

|----------|------|-------|-------|-------|---------|---------------|------------|

| 1 01 11  | 70   | 11011 | 17311 | 00111 | 001 111 | 1111111111111 | 11011 (111 |

**PSPIF:** Parallel Slave Port Read/Write Interrupt Flag bit

1 = A read or a write operation has taken place (must be cleared in software)

0 = No read or write has occurred

**ADIF**: A/D Converter Interrupt Flag bit

1 = An A/D conversion completed

0 = The A/D conversion is not complete

**RCIF**: USART Receive Interrupt Flag bit

1 = The USART receive buffer is full

0 = The USART receive buffer is empty

TXIF: USART Transmit Interrupt Flag bit

1 = The USART transmit buffer is empty

0 = The USART transmit buffer is full

**SSPIF**: Synchronous Serial Port (SSP) Interrupt Flag bit

1 = The SSP interrupt condition has occurred (must be cleared in s/w)

0 = No SSP interrupt condition has occurred

**CCP1IF**: CCP1 Interrupt Flag bit

Capture mode:

1 = A TMR1 register capture occurred

0 = No TMR1 register capture occurred

Compare mode:

1 = A TMR1 register compare match occurred

0 = No TMR1 register compare match occurred

TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred

0 = No TMR2 to PR2 match occurred

**TMR1IF**: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

0 = TMR1 register did not overflow

## PIE2 Register

| _     | CMIE | _ | EEIE | BCLIE | _ | _ | CCP2IE |

|-------|------|---|------|-------|---|---|--------|

| bit 7 | •    | • |      | •     | • | • | bit 0  |

**CMIE**: Comparator Interrupt Enable bit

- 1 = Enables the comparator interrupt

- 0 = Disable the comparator interrupt

**EEIE**: EEPROM Write Operation Interrupt Enable bit

- 1 = Enable EEPROM write interrupt

- 0 = Disable EEPROM write interrupt

**BCLIE**: Bus Collision Interrupt Enable bit

- 1 = Enable bus collision interrupt

- 0 = Disable bus collision interrupt

**CCP2IE**: CCP2 Interrupt Enable bit

- 1 = Enables the CCP2 interrupt

- 0 = Disables the CCP2 interrupt

## PIR2 Register

\_ CMIF \_ EEIF BCLIF \_ \_ CCP2IF

bit 7 bit 0

### **CMIF**: Comparator Interrupt Flag bit

- 1 = The comparator input has changed (must be cleared in s/w)

- 0 = The comparator input has not changed

### **EEIF**: EEPROM Write Operation Interrupt Flag bit

- 1 = The write operation completed (must be cleared in s/w)

- 0 = The write operation is not complete or has not been started

### **BCLIF**: Bus Collision Interrupt Flag bit

- 1 = A bus collision has occurred in the SSP when configured for I2C Master mode

- 0 = No bus collision has occurred

### **CCP2IF**: CCP2 Interrupt Flag bit

### Capture mode:

- 1 = A TMR1 register capture occurred (must be cleared in s/w)

- 0 = No TMR1 register capture occurred

#### Compare mode:

- 1 = A TMR1 register compare match occurred (must be cleared in s/w)

- 0 = No TMR1 register compare match occurred